DivIDE MEMORY

| DivIDE interacts with ZX Spectrum

using I/O accesses or automatically by replacing original ZX-ROM

with its own memory, when CPU fetch from an entry-point is detected (and

such behavior is somehow allowed). DivIDE contains 8 kB ROM (could be not present, EPROM or EEPROM, in the third case it's in-system reprogrammable) and 32-512 kB RAM. DivIDE can use system from 3rd 8k bank of its RAM, this is suitable especially for safe system development. Accidental EEPROM damage (due to unlucky out from crashed code) is fused by the on-board jumper. Memory mapping |

DivIDE in standard mode

DivIDE

control register (write only) 227 ($E3) in original DivIDE

mode:

This register is write-only (readed data will be

unknown). All bits are reset to '0' after each power-on. Unimplemented

bits, marked 'X', should be zeroed for future compatibility issues with

more than 32kB RAM DivIDEs. |

| value

10xxxxBB Bit CONMEM forces EPROM/EEPROM to 0000-1fffh and by BANK 1..0 selected bank to area 2000-3fffh, regardless to the actual divIDE state or to physical presence of EPROM/EEPROM. Bank in area 2000-3fffh is always writable, and in 0000-1fffh always appears EEPROM/EPROM, which is writable when EPROM jumper is open. Use it in third-party utilities for loading system or modules, or in system's auto-upgrade process.

|

| value

01xxxxBB (with closed jumper E) Bit MAPRAM can be set to '1' only (when it's '1', only power-on can return it to '0'). This bit allows 8k bank No.3 to act as EPROM/EEPROM, and write-protects it. Set it when system image is loaded into bank No.3 and you want to safe probe it till the next power-on. Set it also when you haven't EPROM/EEPROM, and you want to use system. (Because u will possibly re-install it from MAPRAM mode, you will need CONMEM to override writeprotect. Because after returning to BASIC you rely on original ROM, you must reset automapper, which could be left in undesired state by previous bus transactions. Because it could be done only by fetching code from off-area, u must set DI, then call 1ffbh ('RET'), ten CONMEM, loading image, releasing CONMEM and setting MAPRAM, then EI. Then the return is safe.)

|

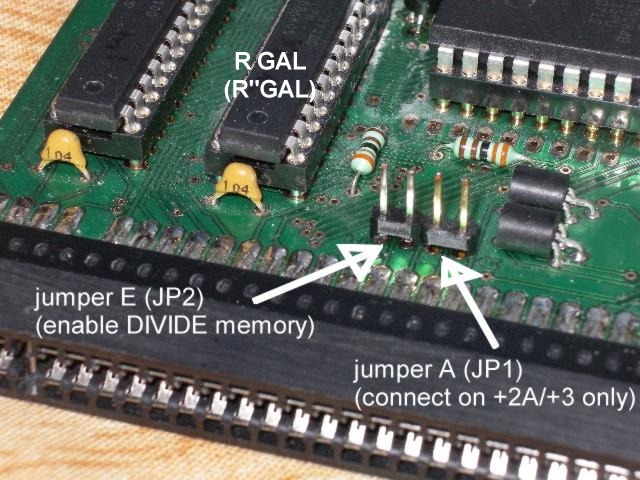

DivIDE with allram mode support (with R"GAL

chip)

DivIDE

control register (write only) 227 ($E3) before allram

activation (original DivIDE mode):

This all instructions must be writed in assembler

with disable IM1 interrupt (ZX rom will disconnect):

If jumper JP2 (E) is closed, then DivIDE will switched to original mode (with active mapram). |

| NMI

button in allram mode In allram mode don't work divide automapper, but NMI button will disabled if CPU read instruction opcode from adress 0000h, 0008h, 0038h, 0066h, 04c6h, 0562h and 3D00h-3DFFh. NMI is automatically enabled in refresh cycle of the instruction fetch from so called off-area, which is 1ff8-1fffh. This feature is used in new version of BS-DOS system for DivIDE. |

| DOWNLOAD new R"GAL chip firmware |

| R"GAL - new GAL version with new allram mode support |

| R GAL - original (old) GAL version without allram mode |

|

Allram feature is available

only on DivIDE interface with new R"GAL chip. DivIDE with this GAL is

possible buy at DIVIDE

SHOP. Old DivIDE interface can be also upgraded if you replace R-GAL

chip with new R"GAL (possible buy in same shop)